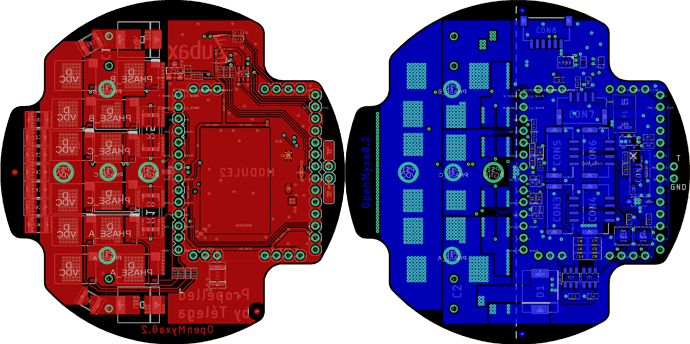

PCB and construction

At this point, it is crucial to have some physical representation of the final result: at least the overall shape, dimensions and connector placement should be known by this time.

Two main questions to address when designing power electronics and supercomputers are:

- How does one deliver all the necessary power to the device without substantive power losses?

- How does one cool everything that heats up?

Both of these questions have a direct relationship to the power stage PCB design. Routing high currents through the PCB is generally not the best idea as the copper foil thickness is typically in the range of 0.035 – 0.105 mm (n.b. thicker foil imposes more restrictions on the PCB design due to the limitations of the PCB manufacturing process). There is an upper limit to the amount of current that can be routed conventionally through a regular FR4 PCB; as an oversimplified rule of thumb, this limit is between 50 – 100 A. Anything above this limit would require special measures (e.g. busbars, PCB trace reinforcement, etc.).

Fortunately, Komar’s maximum phase current allows it to be routed on a regular PCB, although it still requires the power stage to be properly designed. The key element here is the component arrangement. The designer should minimize the path of high current through the PCB (if high current barely touches the PCB copper, it can’t influence the PCB too much). All the connections that carry high currents should be made with polygons to ensure that the electrical resistance is minimized. Polygons also serve as heat distributors, removing heat from transistors (and other heating components) and spreading across the PCB. This in turn increases the effective contact area between the PCB and the heatsink. It should be noted that the transistor’s R_\text{DS(on)} is a temperature-dependent parameter, which is why it is important to ensure that the thermal load is distributed equally across the transistors. This is the second role of big polygons: they should couple all the transistors thermally together.

The second important design challenge, after providing a good path for the power input, is cooling. There is more than one way to cool electronic components but the simplest and most cost-effective one is air-cooling. Usually, some kind of heatsink that dissipates heat into the environment is suggested. First, though, the heat needs to be transferred to the heatsink. The designer should minimize the thermal resistance between the transistors’ junctions and the heatsink.

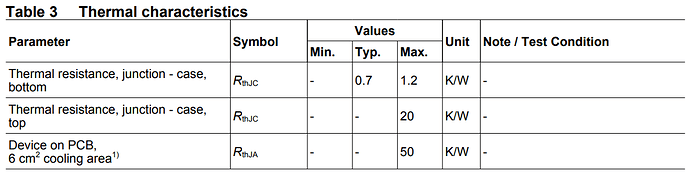

As an example, Komar uses power transistors in the PowerTDFN-8 package. Its thermal resistance is described in the following table:

It should be obvious that the heat from the transistors is transferred much more efficiently to the PCB through the bottom of the transistor housing than through the top. When heat is transferred to the top side of the PCB it should be transferred onward to the bottom side and then to the heatsink. Multiple via holes help the heat to get to the bottom side of the PCB. The exact thermal impedance of a via depends on the PCB manufacturing process, the via’s diameter, and the PCB’s thickness. Here is a good article on the topic:

https://www.electronics-cooling.com/2004/08/thermal-vias-a-packaging-engineers-best-friend/

Long story short, many smaller vias perform considerably better than fewer bigger ones because it is the total surface area of metal connecting the two sides of the PCB that matters. Consequently, it is highly recommended to fit as many vias as possible on the transistors footprints and position them for best thermal performance. The only practical way of transferring the heat onward to the heatsink is just to press the heatsink to the PCB mechanically. Of course, this requires that there are no components on the bottom side of the PCB (or at least, there are no components directly under the transistors).

Important note: In most cases, the heatsink is not directly attached to the PCB (or other objects that needs cooling) but through some kind of thermal pad. In the case of Komar, a thermal pad is needed because there are many different signals and polygons on the bottom side of the PCB and as the soldering mask is not a proper insulation something may short. The designer should keep in mind that thermal pads may have drastically different thermal resistance so care is needed in selecting one. The second important consideration is that thermal pads are specified under pretty strict conditions, the most important of which is pressure. You may pick the best thermal pad available to a mortal man but if you don’t provide it with the specified pressure, it won’t perform any good. Of course, this matter does not relate to the PCB routing directly but it still has to be mentioned.

The worst-case power losses in the power stage are calculated next. First, the maximum power loss for one individual switch are calculated, where by “switch” we refer to a group of transistors forming an inverter node (in our case, that would be two transistors in parallel). The coefficients next to the loss components account for the fact that normally, only 4 of the 6 switches are switching (of the other two, one is constantly closed and one is constantly conducting DC) and at any given moment only 3 switches out of 6 are conducting:

where:

- F_\text{switch} = 47 000\text{ Hz}

- V_\text{dc} = 50.2\text{ V}

- I_\text{rms} = \frac{65\text{ A}}{\sqrt{2}} (the peak phase current flowing through one switch is 65 A)

- T_\text{rise} = 50 \times 10^{-9}\text{ s}

- T_\text{fall} = 50 \times 10^{-9}\text{ s}

- R_\text{DS(on)} is that of the switch rather than an individual transistor (twice lower in our case)

Now the total power stage losses can be calculated using the power loss in a single switch along with the losses in the current shunts that were found earlier:

This is an approximation because many system parameters are temperature-dependent and are, therefore, constantly changing. We are also not considering losses through the flyback diodes, as they are typically quite low in a well-designed modern inverter with tight dead times (n.b.: Mitochondrik controls the dead time automatically in hardware).

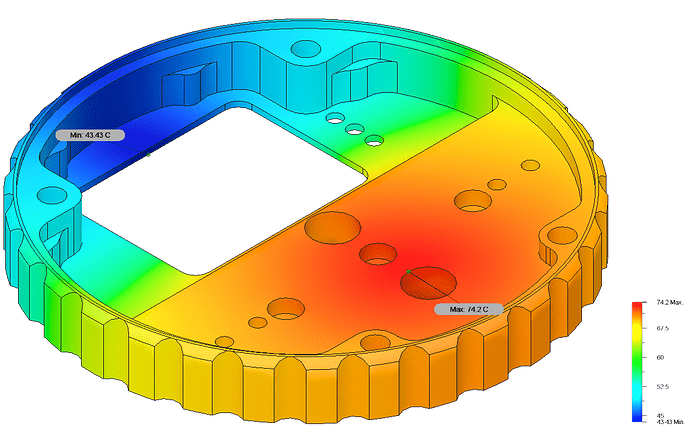

The last thing needed for the thermal simulation is the convection rate. This is a tricky one and usually has to be picked from existing convection tables. For forced-air convection, the rate may be 300\ \frac{W}{m^2 K} depending on the intensity of the airflow around the heat sink.

For the sake of simplicity, the simulation does not involve the actual PCB with transistors. It is just about the ability of the heatsink to dissipate the rejected energy under the specified convection rate. It is seen that the temperature gradient is moderate (especially considering the shape of the object) and the maximum temperature is below 80°C. One should keep in mind that the actual temperature of the semiconductor crystals will be higher than the temperature of the heatsink due to the non-zero thermal impedance between the crystals and the heatsink (n.b. this difference may exceed 50°C).

All the reasoning above indicates that with a device like Komar, it is possible to sustain continuous operation at the power levels as high as 2.5 kW. Further confirmation would require prototype manufacturing and testing on actual hardware. These tests have been conducted and the results were found to be sufficiently similar to the model predictions.

All the hardware source files can be found in the GitHub repository.